### 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

### **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

### W681513

# 5V SINGLE-CHANNEL VOICEBAND CODEC FOR USB APPLICATIONS

### **Data Sheet**

Publication Release Date: October, 2005 Revision A11

- 1 -

#### 1. GENERAL DESCRIPTION

The W681513 is a single channel PCM CODEC with pin-selectable  $\mu$ -Law or A-Law companding dedicated to the USB accessory market by supporting a derivative 2MHz clock. The device is compliant with the ITU G.712 specification. It operates from a single +5V power supply and is available in 20-pin SOP package option. Functions performed include digitization and reconstruction of voice signals, and band limiting and smoothing filters required for PCM systems. The filters are compliant with ITU G.712 specification. W681513 performance is specified over the industrial temperature range of -40°C to +85°C.

The W681513 includes an on-chip precision voltage reference and an additional power amplifier, capable of driving  $300\Omega$  loads differentially up to a level of 6.3V peak-to-peak. The analog section is fully differential, reducing noise and improving the power supply rejection ratio. The data transfer protocol supports both long-frame and short-frame synchronous communications for PCM applications, and IDL and GCI communications for ISDN applications. W681513 accepts 2MHz master clock rate, and an on-chip pre-scaler automatically determines the division ratio for the required internal clock.

#### 2. FEATURES

- Single +5V power supply

- Typical power dissipation of 30 mW, power-down mode of 0.5 μW

- Fully-differential analog circuit design

- On-chip precision reference of 1.575 V for a 0 dBm TLP at 600 Ω (775mV<sub>RMS</sub>)

- Push-pull power amplifiers with external gain adjustment with 300  $\Omega$  load capability

- Master clock rate supports 2.000MHz clock for USB applications

- Pin-selectable μ-Law and A-Law companding (compliant with ITU G.711)

- CODEC A/D and D/A filtering compliant with ITU G.712

- Industrial temperature range (-40°C to +85°C)

- Package: 20-pin SOP (SOG)

- Pb-Free / RoHS package option available

### **Applications**

- Soft phones running on a PC (VoInternet):

- USB Phones

- USB to PSTN Gateway

- USB Microphones

- USB Headset for PC and Game Consoles

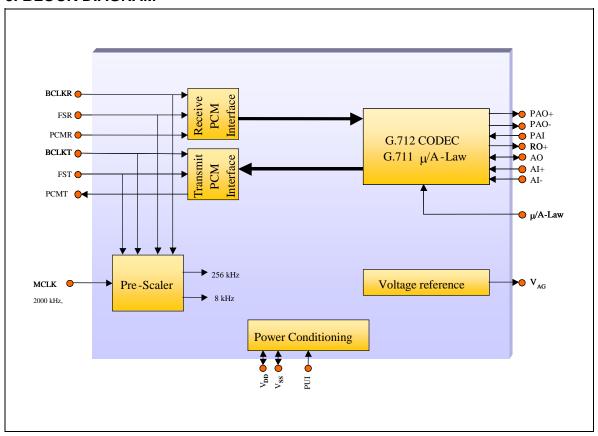

### 3. BLOCK DIAGRAM

### W681513

# **Esses winbond Esses**

| 4 | T A |    |   | $\sim$ $\sim$    | $\sim$ |   | ,     | NTS   |

|---|-----|----|---|------------------|--------|---|-------|-------|

| 4 | ΙΔ  | KI | _ | ( ) <del>-</del> | (:()   | N | і — г | u 1 S |

|   |     |    |   |                  |        |   |       |       |

| 1. GENERAL DESCRIPTION                             | 2  |

|----------------------------------------------------|----|

| 2. FEATURES                                        | 2  |

| 3. BLOCK DIAGRAM                                   | 3  |

| 4. TABLE OF CONTENTS                               | 4  |

| 5. PIN CONFIGURATION                               | 6  |

| 6. PIN DESCRIPTION                                 | 7  |

| 7. FUNCTIONAL DESCRIPTION                          | 8  |

| 7.1. Transmit Path                                 | 8  |

| 7.2. Receive Path                                  | 9  |

| 7.3. Power Management                              | 10 |

| 7.3.1. Analog and Digital Supply                   | 10 |

| 7.3.2. Analog Ground Reference Voltage Outpt       | 10 |

| 7.4. PCM Interface                                 | 10 |

| 7.4.1. Long Frame Sync                             | 10 |

| 7.4.2. Short Frame Sync                            | 11 |

| 7.4.3. General Circuit Interface (GCI)             | 11 |

| 7.4.4. Interchip Digital Link (IDL)                | 12 |

| 7.4.5. System Timing                               | 12 |

| 8. TIMING DIAGRAMS                                 | 13 |

| 9. ABSOLUTE MAXIMUM RATIINGS                       | 20 |

| 9.1. Absolute Maximum Ratings                      | 20 |

| 9.2. Operating Conditions                          | 20 |

| 10. ELECTRICAL CHARACTERISTICS                     | 21 |

| 10.1. General Parameters                           | 21 |

| 10.2. Analog Signal Level and Gain Parameters      | 22 |

| 10.3. Analog Distortion and Noise Parameters       | 23 |

| 10.4. Analog Input and Output Amplifier Parameters | 24 |

| 10.5. Digital I/O                                  | 26 |

| 10.5.1. μ-Law Encode Decode Characteristics        | 26 |

| 10.5.2. A-Law Encode Decode Characteristics        | 27 |

| 10.5.3. PCM Codes for Zero and Full Scale          | 28 |

| 10.5.4. PCM Codes for 0dBm0 Output                 | 28 |

| 11. TYPICAL APPLICATION CIRCUITS                   | 29 |

| 12. PACKAGE SPECIFICATION                          | 32 |

| 12.2. 20L SOP (SOG)-300mil                         | 32 |

### W681513

# 13. ORDERING INFORMATION 33 14. VERSION HISTORY 34

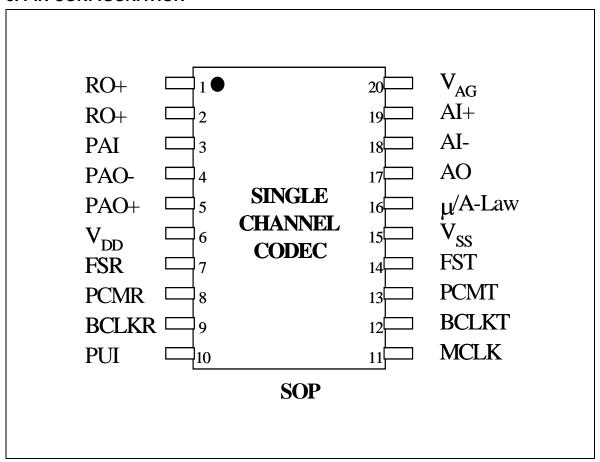

### 5. PIN CONFIGURATION

### W681513

### 6. PIN DESCRIPTION

| Pin             | Pin | Functionality                                                                                                                                                                                                                                                                                                   |

|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | No. |                                                                                                                                                                                                                                                                                                                 |

| RO+             | 1   | Non-inverting output of the receive smoothing filter. This pin can typically drive a 2 k $\Omega$ load to 1.575 volt peak referenced to the analog ground level.                                                                                                                                                |

| RO+             | 2   | Non-inverting output of the receive smoothing filter. This pin can typically drive a 2 k $\Omega$ load to 1.575 volt peak referenced to the analog ground level.                                                                                                                                                |

| PAI             | 3   | This pin is the inverting input to the power amplifier. Its DC level is at the V <sub>AG</sub> voltage.                                                                                                                                                                                                         |

| PAO-            | 4   | Inverting power amplifier output. This pin can drive a 300 $\Omega$ load to 1.575 volt peak referenced to the $V_{AG}$ voltage level.                                                                                                                                                                           |

| PAO+            | 5   | Non-inverting power amplifier output. This pin can drive a 300 $\Omega$ load to 1.575 volt peak referenced to the $V_{AG}$ voltage level.                                                                                                                                                                       |

| $V_{DD}$        | 6   | Power supply. This pin should be decoupled to $V_{SS}$ with a $0.1\mu F$ ceramic capacitor.                                                                                                                                                                                                                     |

| FSR             | 7   | 8 kHz Frame Sync input for the PCM receive section. This pin also selects channel 0 or channel 1 in the GCI and IDL modes. It can also be connected to the FST pin when transmit and receive are synchronous operations.                                                                                        |

| PCMR            | 8   | PCM input data receive pin. The data needs to be synchronous with the FSR and BCLKR pins.                                                                                                                                                                                                                       |

| BCLKR           | 9   | PCM receive bit clock input pin. This pin also selects the interface mode. The GCI mode is selected when this pin is tied to $V_{\text{SS}}$ . The IDL mode is selected when this pin is tied to $V_{\text{DD}}$ . This pin can also be tied to the BCLKT when transmit and receive are synchronous operations. |

| PUI             | 10  | Power up input signal. When this pin is tied to $V_{\text{DD}}$ , the part is powered up. When tied to $V_{\text{SS}}$ , the part is powered down.                                                                                                                                                              |

| MCLK            | 11  | System master clock input supporting 2000 kHz only.                                                                                                                                                                                                                                                             |

| BCLKT           | 12  | PCM transmit bit clock input pin.                                                                                                                                                                                                                                                                               |

| PCMT            | 13  | PCM output data transmit pin. The output data is synchronous with the FST and BCLKT pins.                                                                                                                                                                                                                       |

| FST             | 14  | 8 kHz transmit frame sync input. This pin synchronizes the transmit data bytes.                                                                                                                                                                                                                                 |

| V <sub>SS</sub> | 15  | This is the supply ground. This pin should be connected to 0V.                                                                                                                                                                                                                                                  |

| μ/A-Law         | 16  | Compander mode select pin. $\mu$ -Law companding is selected when this pin is tied to $V_{DD}$ . A-Law companding is selected when this pin is tied to $V_{SS}$ .                                                                                                                                               |

| AO              | 17  | Analog output of the first gain stage in the transmit path.                                                                                                                                                                                                                                                     |

| Al-             | 18  | Inverting input of the first gain stage in the transmit path.                                                                                                                                                                                                                                                   |

| Al+             | 19  | Non-inverting input of the first gain stage in the transmit path.                                                                                                                                                                                                                                               |

| V <sub>AG</sub> | 20  | Mid-Supply analog ground pin, which supplies a 2.5 Volt reference voltage for all-analog signal processing. This pin should be decoupled to $V_{SS}$ with a $0.01\mu F$ to $0.1~\mu F$ capacitor. This pin becomes high impedance when the chip is powered down.                                                |

#### 7. FUNCTIONAL DESCRIPTION

W681513 is a single-rail, single channel PCM CODEC for voiceband applications. The CODEC complies with the specifications of the ITU-T G.712 recommendation. The CODEC also includes a complete  $\mu$ -Law and A-Law compander. The  $\mu$ -Law and A-Law companders are designed to comply with the specifications of the ITU-T G.711 recommendation.

The block diagram in section 3 shows the main components of the W681513. The chip consists of a PCM interface, which can process long and short frame sync formats, as well as GCI and IDL formats. The pre-scaler of the chip provides the internal clock signals and synchronizes the CODEC sample rate with the external frame sync frequency. The power conditioning block provides the internal power supply for the digital and the analog section, while the voltage reference block provides a precision analog ground voltage for the analog signal processing. The main CODEC block diagram is shown in section 3.

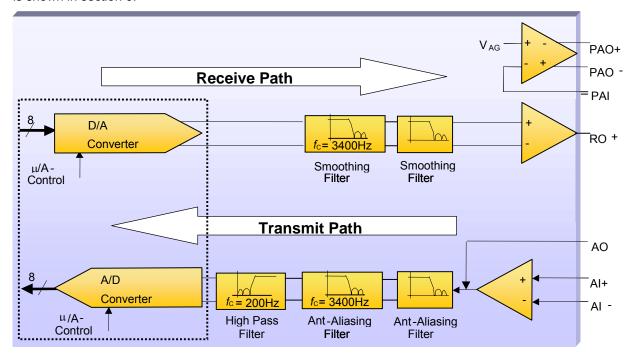

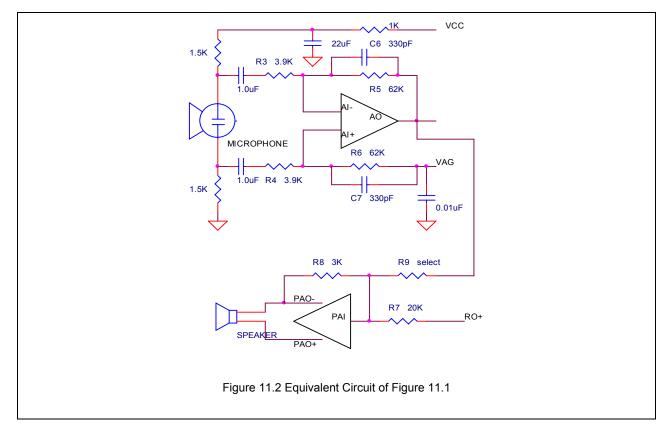

Figure 7.1 The W681513 Signal Path

### 7.1. Transmit Path

The A-to-D path of the CODEC contains an analog input amplifier with externally configurable gain setting (see application examples in section 11). The device has an input operational amplifier whose output is the input to the encoder section. If the input amplifier is not required for operation it can be powered down and bypassed. In that case a single ended input signal can be applied to the AO pin or the AI- pin. The AO pin becomes high input impedance when the input amplifier is powered down. The input amplifier can be powered down by connecting the AI+ pin to  $V_{DD}$  or  $V_{SS}$ . The AO pin is selected

as an input when AI+ is tied to  $V_{DD}$  and the AI- pin is selected as an input when AI+ is tied to  $V_{SS}$  (see Table 7.1).

| AI+                         | Input Amplifier | Input    |

|-----------------------------|-----------------|----------|

| V <sub>DD</sub>             | Powered Down    | AO       |

| 1.2 to V <sub>DD</sub> -1.2 | Powered Up      | Al+, Al- |

| V <sub>SS</sub>             | Powered Down    | Al-      |

Table 7.1 Input Amplifier Modes of operation

When the input amplifier is powered down, the input signal at AO or AI- needs to be referenced to the analog ground voltage  $V_{AG}$ .

The output of the input amplifier is fed through a low-pass filter to prevent aliasing at the switched capacitor 3.4 kHz low pass filter. The 3.4 kHz switched capacitor low pass filter prevents aliasing of input signals above 4 kHz, due to the sampling at 8 kHz. The output of the 3.4 kHz low pass filter is filtered by a high pass filter with a 200 Hz cut-off frequency. The filters are designed according to the recommendations in the G.712 ITU-T specification. From the output of the high pass filter the signal is digitized. The signal is converted into a compressed 8-bit digital representation with either  $\mu$ -Law or A-Law format. The  $\mu$ -Law or A-Law format is pin-selectable through the  $\mu$ /A-Law pin. The compression format can be selected according to Table 7.2.

| μ/A-Law Pin     | Format |

|-----------------|--------|

| V <sub>SS</sub> | A-Law  |

| $V_{DD}$        | μ-Law  |

Table 7.2. Pin-selectable Compression Format

The digital 8-bit  $\mu$ -Law or A-Law samples are fed to the PCM interface for serial transmission at the sample rate supplied by the external frame sync FST.

#### 7.2. Receive Path

The 8-bit digital input samples for the D-to-A path are serially shifted in by the PCM interface and converted to parallel data bits. During every cycle of the frame sync FSR, the parallel data bits are fed through the pin-selectable  $\mu$ -Law or A-Law expander and converted to analog samples. The mode of expansion is selected by the  $\mu$ /A-Law pin as shown in Table 7.2. The analog samples are filtered by a low-pass smoothing filter with a 3.4 kHz cut-off frequency, according to the ITU-T G.712 specification. A sin(x)/x compensation is integrated with the low pass smoothing filter. The output of this filter is buffered to provide the receive output signal RO+. The RO+ output can be externally connected to the PAI pin to provide a differential output with high driving capability at the PAO+ and PAO- pins. By using external resistors (see section 11 for examples), various gain settings of this output amplifier

can be achieved. If the transmit power amplifier is not in use, it can be powered down by connecting PAI to  $V_{\text{DD}}$ .

#### 7.3. POWER MANAGEMENT

### 7.3.1. Analog and Digital Supply

The power supply for the analog and digital parts of the W681513 must be 5V +/- 10%. This supply voltage is connected to the  $V_{DD}$  pin. The  $V_{DD}$  pin needs to be decoupled to ground through a 0.1  $\mu$ F ceramic capacitor.

### 7.3.2. Analog Ground Reference Voltage Output

The analog ground reference voltage is available for external reference at the  $V_{AG}$  pin. This voltage needs to be decoupled to  $V_{SS}$  through a 0.01  $\mu F$  ceramic capacitor.

#### 7.4. PCM INTERFACE

The PCM interface is controlled by pins BCLKR, FSR, BCLKT & FST. The input data is received through the PCMR pin and the output data is transmitted through the PCMT pin. The modes of operation of the interface are shown in Table 7.3.

| BCLKR           | FSR             | Interface Mode                  |

|-----------------|-----------------|---------------------------------|

| 2.000 MHz       | 8 kHz           | Long or Short Frame Sync        |

| V <sub>SS</sub> | V <sub>SS</sub> | ISDN GCI with active channel B1 |

| V <sub>SS</sub> | $V_{DD}$        | ISDN GCI with active channel B2 |

| V <sub>DD</sub> | V <sub>SS</sub> | ISDN IDL with active channel B1 |

| $V_{DD}$        | $V_{DD}$        | ISDN IDL with active channel B2 |

Table 7.3 PCM Interface mode selections

#### 7.4.1. Long Frame Sync

The Long Frame Sync or Short Frame Sync interface mode can be selected by connecting the BCLKR or BCLKT pin to a 2.000 MHz clock and connecting the FSR or FST pin to the 8 kHz frame sync. The device synchronizes the data word for the PCM interface and the CODEC sample rate on the positive edge of the Frame Sync signal. It recognizes a Long Frame Sync when the FST pin is

held HIGH for two consecutive falling edges of the bit-clock at the BCLKT pin. The length of the Frame Sync pulse can vary from frame to frame, as long as the positive frame sync edge occurs every 125  $\mu sec.$  During data transmission in the Long Frame Sync mode, the transmit data pin PCMT will become low impedance when the Frame Sync signal FST is HIGH or when the 8 bit data word is being transmitted. The transmit data pin PCMT will become high impedance when the Frame Sync signal FST becomes LOW while the data is transmitted or when half of the LSB is transmitted. The internal decision logic will determine whether the next frame sync is a long or short frame sync, based on the previous frame sync pulse. To avoid bus collisions, the PCMT pin will be high impedance for two frame sync cycles after every power down state. More detailed timing information can be found in the interface timing section.

### 7.4.2. Short Frame Sync

The W681513 operates in the Short Frame Sync Mode when the Frame Sync signal at pin FST is HIGH for one and only one falling edge of the bit-clock at the BCLKT pin. On the following rising edge of the bit-clock, the W681513 starts clocking out the data on the PCMT pin, which will also change from high to low impedance state. The data transmit pin PCMT will go back to the high impedance state halfway through the LSB. The Short Frame Sync operation of the W681513 is based on an 8-bit data word. When receiving data on the PCMR pin, the data is clocked in on the first falling edge after the falling edge that coincides with the Frame Sync signal. The internal decision logic will determine whether the next frame sync is a long or short frame sync, based on the previous frame sync pulse. To avoid bus collisions, the PCMT pin will be high impedance for two frame sync cycles after every power down state. More detailed timing information can be found in the interface timing section.

#### 7.4.3. General Circuit Interface (GCI)

The GCI interface mode is selected when the BCLKR pin is connected to  $V_{\rm SS}$  for two or more frame sync cycles. It can be used as a 2B+D timing interface in an ISDN application. The GCI interface consists of 4 pins: FSC (FST), DCL (BCLKT), Dout (PCMT) & Din (PCMR). The FSR pin selects channel B1 or B2 for transmit and receive. Data transitions occur on the positive edges of the data clock DCL. The Frame Sync positive edge is aligned with the positive edge of the data clock DCLK. The data rate is running half the speed of the bit-clock. The channels B1 and B2 are transmitted consecutively. Therefore, channel B1 is transmitted on the first 16 clock cycles of DCL and B2 is transmitted on the second 16 clock cycles of DCL. For more timing information, see the timing section.

### 7.4.4. Interchip Digital Link (IDL)

The IDL interface mode is selected when the BCLKR pin is connected to  $V_{\text{DD}}$  for two or more frame sync cycles. It can be used as a 2B+D timing interface in an ISDN application. The IDL interface consists of 4 pins: IDL SYNC (FST), IDL CLK (BCLKT), IDL TX (PCMT) & IDL RX (PCMR). The FSR pin selects channel B1 or B2 for transmit and receive. The data for channel B1 is transmitted on the first positive edge of the IDL CLK after the IDL SYNC pulse. The IDL SYNC pulse is one IDL CLK cycle long. The data for channel B2 is transmitted on the eleventh positive edge of the IDL CLK after the IDL SYNC pulse. The data for channel B1 is received on the first negative edge of the IDL CLK after the IDL SYNC pulse. The data for channel B2 is received on the eleventh negative edge of the IDL CLK after the IDL SYNC pulse. The transmit signal pin IDL TX becomes high impedance when not used for data transmission and also in the time slot of the unused channel. For more timing information, see the timing section.

### 7.4.5. System Timing

The system can work at 2000 kHz master clock rate only. The system clock is supplied through the master clock input MCLK and can be derived from the bit-clock if desired. An internal pre-scaler is used to generate a fixed 256 kHz and 8 kHz sample clock for the internal CODEC. If the Frame Sync is LOW for the entire frame sync period while the MCLK and BCLK pin clock signals are still present, the W681513 will enter the low power standby mode. Another way to power down is to set the PUI pin to low. When the system needs to be powered up again, the PUI pin needs to be set to HIGH and the Frame Sync pulse needs to be present. It will take two Frame Sync cycles before the pin PCMT will become low impedance.

# **Tables winbond seess**

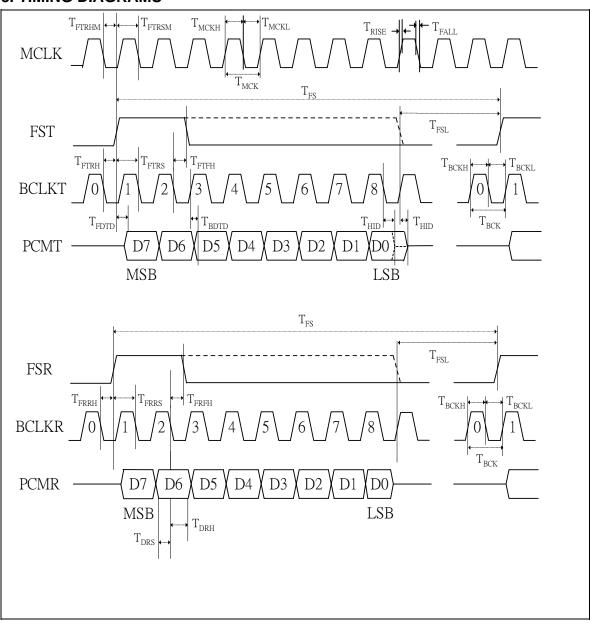

### 8. TIMING DIAGRAMS

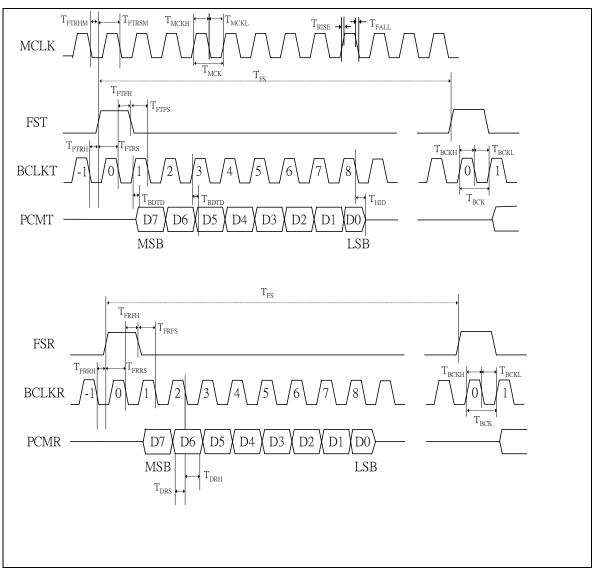

Figure 8.1 Long Frame Sync PCM Timing

# \_\_\_\_winbond

| SYMBOL             | DESCRIPTION                                        | MIN              | TYP | MAX  | UNIT |

|--------------------|----------------------------------------------------|------------------|-----|------|------|

| 1/T <sub>FS</sub>  | FST, FSR Frequency                                 |                  | 8   |      | kHz  |

| T <sub>FSL</sub>   | FST / FSR Minimum LOW Width <sup>1</sup>           | T <sub>BCK</sub> |     |      | sec  |

| 1/T <sub>BCK</sub> | BCLKT, BCLKR Frequency                             | 2000             |     | 2000 | kHz  |

| T <sub>BCKH</sub>  | BCLKT, BCLKR HIGH Pulse Width                      | 50               |     |      | ns   |

| T <sub>BCKL</sub>  | BCLKT, BCLKR LOW Pulse Width                       | 50               |     |      | ns   |

| T <sub>FTRH</sub>  | BCLKT 0 Falling Edge to FST Rising Edge Hold Time  | 20               |     |      | ns   |

| T <sub>FTRS</sub>  | FST Rising Edge to BCLKT 1 Falling edge Setup Time | 80               |     |      | ns   |

| T <sub>FTFH</sub>  | BCLKT 2 Falling Edge to FST Falling Edge Hold Time | 50               |     |      | ns   |

| T <sub>FDTD</sub>  | FST Rising Edge to Valid PCMT Delay Time           |                  |     | 60   | ns   |

| T <sub>BDTD</sub>  | BCLKT Rising Edge to Valid PCMT Delay Time         |                  |     | 60   | ns   |

| T <sub>HID</sub>   | Delay Time from the Later of FST Falling Edge, or  | 10               |     | 60   | ns   |

|                    | BCLKT 8 Falling Edge to PCMT Output High Impedance |                  |     |      |      |

| T <sub>FRRH</sub>  | BCLKR 0 Falling Edge to FSR Rising Edge Hold Time  | 20               |     |      | ns   |

| T <sub>FRRS</sub>  | FSR Rising Edge to BCLKR 1 Falling edge Setup Time | 80               |     |      | ns   |

| T <sub>FRFH</sub>  | BCLKR 2 Falling Edge to FSR Falling Edge Hold Time | 50               |     |      | ns   |

| T <sub>DRS</sub>   | Valid PCMR to BCLKR Falling Edge Setup Time        | 0                |     |      | ns   |

| T <sub>DRH</sub>   | PCMR Hold Time from BCLKR Falling Edge             | 50               |     |      | ns   |

Table 8.1 Long Frame Sync PCM Timing Parameters

$<sup>^{1}</sup>$  T<sub>FSL</sub> must be at least  $\geq$  T<sub>BCK</sub>

# winbond.

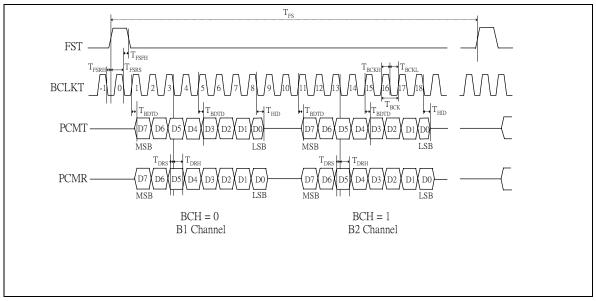

Figure 8.2 Short Frame Sync PCM Timing

### W681513

# \_\_\_winbond

| SYMBOL             | DESCRIPTION                                                        | MIN  | TYP | MAX  | UNIT |

|--------------------|--------------------------------------------------------------------|------|-----|------|------|

| 1/T <sub>FS</sub>  | FST, FSR Frequency                                                 |      | 8   |      | kHz  |

| 1/T <sub>BCK</sub> | BCLKT, BCLKR Frequency                                             | 2000 |     | 2000 | kHz  |

| T <sub>BCKH</sub>  | BCLKT, BCLKR HIGH Pulse Width                                      | 50   |     |      | ns   |

| T <sub>BCKL</sub>  | BCLKT, BCLKR LOW Pulse Width                                       | 50   |     |      | ns   |

| T <sub>FTRH</sub>  | BCLKT –1 Falling Edge to FST Rising Edge Hold Time                 | 20   |     |      | ns   |

| T <sub>FTRS</sub>  | FST Rising Edge to BCLKT 0 Falling edge Setup Time                 | 80   |     |      | ns   |

| T <sub>FTFH</sub>  | BCLKT 0 Falling Edge to FST Falling Edge Hold Time                 | 50   |     |      | ns   |

| T <sub>FTFS</sub>  | FST Falling Edge to BCLKT 1 Falling Edge Setup Time                | 50   |     |      | ns   |

| T <sub>BDTD</sub>  | BCLKT Rising Edge to Valid PCMT Delay Time                         | 10   |     | 60   | ns   |

| T <sub>HID</sub>   | Delay Time from BCLKT 8 Falling Edge to PCMT Output High Impedance | 10   |     | 60   | ns   |

| T <sub>FRRH</sub>  | BCLKR –1 Falling Edge to FSR Rising Edge Hold Time                 | 20   |     |      | ns   |

| T <sub>FRRS</sub>  | FSR Rising Edge to BCLKR 0 Falling edge Setup Time                 | 80   |     |      | ns   |

| T <sub>FRFH</sub>  | BCLKR 0 Falling Edge to FSR Falling Edge Hold Time                 | 50   |     |      | ns   |

| T <sub>FRFS</sub>  | FSR Falling Edge to BCLKR 1 Falling Edge Setup Time                | 50   |     |      | ns   |

| T <sub>DRS</sub>   | Valid PCMR to BCLKR Falling Edge Setup Time                        | 0    |     |      | ns   |

| T <sub>DRH</sub>   | PCMR Hold Time from BCLKR Falling Edge                             | 50   |     |      | ns   |

Table 8.2 Short Frame Sync PCM Timing Parameters

# winbond

Figure 8.3 IDL PCM Timing

| SYMBOL             | DESCRIPTION                                                                                                               | MIN  | TYP | MAX  | UNIT |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| 1/T <sub>FS</sub>  | FST Frequency                                                                                                             |      | 8   |      | kHz  |

| 1/T <sub>BCK</sub> | BCLKT Frequency                                                                                                           | 2000 |     | 2000 | kHz  |

| T <sub>BCKH</sub>  | BCLKT HIGH Pulse Width                                                                                                    | 50   |     |      | ns   |

| T <sub>BCKL</sub>  | BCLKT LOW Pulse Width                                                                                                     | 50   |     |      | ns   |

| T <sub>FSRH</sub>  | BCLKT –1 Falling Edge to FST Rising Edge Hold Time                                                                        | 20   |     |      | ns   |

| T <sub>FSRS</sub>  | FST Rising Edge to BCLKT 0 Falling edge Setup Time                                                                        | 60   |     |      | ns   |

| T <sub>FSFH</sub>  | BCLKT 0 Falling Edge to FST Falling Edge Hold Time                                                                        | 20   |     |      | ns   |

| $T_{BDTD}$         | BCLKT Rising Edge to Valid PCMT Delay Time                                                                                | 10   |     | 60   | ns   |

| T <sub>HID</sub>   | Delay Time from the BCLKT 8 Falling Edge (B1 channel) or BCLKT 18 Falling Edge (B2 Channel) to PCMT Output High Impedance | 10   |     | 50   | ns   |

| T <sub>DRS</sub>   | Valid PCMR to BCLKT Falling Edge Setup Time                                                                               | 20   |     |      | ns   |

| T <sub>DRH</sub>   | PCMR Hold Time from BCLKT Falling Edge                                                                                    | 75   |     |      | ns   |

Table 8.3 IDL PCM Timing Parameters

### winbond a

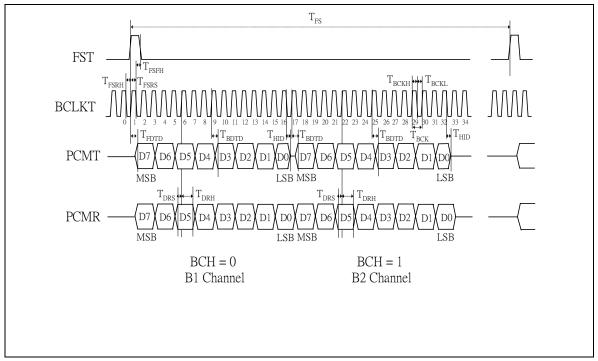

Figure 8.4 GCI PCM Timing

| SYMBOL             | DESCRIPTION                                                                                                                | MIN  | TYP | MAX  | UNIT |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| 1/T <sub>FST</sub> | FST Frequency                                                                                                              |      | 8   |      | kHz  |

| 1/T <sub>BCK</sub> | BCLKT Frequency                                                                                                            | 2000 |     | 2000 | kHz  |

| T <sub>BCKH</sub>  | BCLKT HIGH Pulse Width                                                                                                     | 50   |     |      | ns   |

| T <sub>BCKL</sub>  | BCLKT LOW Pulse Width                                                                                                      | 50   |     |      | ns   |

| T <sub>FSRH</sub>  | BCLKT 0 Falling Edge to FST Rising Edge Hold Time                                                                          | 20   |     |      | ns   |

| T <sub>FSRS</sub>  | FST Rising Edge to BCLKT 1 Falling edge Setup Time                                                                         | 60   |     |      | ns   |

| T <sub>FSFH</sub>  | BCLKT 1 Falling Edge to FST Falling Edge Hold Time                                                                         | 20   |     |      | ns   |

| T <sub>FDTD</sub>  | FST Rising Edge to Valid PCMT Delay Time                                                                                   |      |     | 60   | ns   |

| T <sub>BDTD</sub>  | BCLKT Rising Edge to Valid PCMT Delay Time                                                                                 |      |     | 60   | ns   |

| T <sub>HID</sub>   | Delay Time from the BCLKT 16 Falling Edge (B1 channel) or BCLKT 32 Falling Edge (B2 Channel) to PCMT Output High Impedance | 10   |     | 50   | ns   |

| T <sub>DRS</sub>   | Valid PCMR to BCLKT Rising Edge Setup Time                                                                                 | 20   |     |      | ns   |

| T <sub>DRH</sub>   | PCMR Hold Time from BCLKT Rising Edge                                                                                      |      |     | 60   | ns   |

Table 8.4 GCI PCM Timing Parameters

### W681513

# **Esses winbond Esses**

| SYMBOL                               | DESCRIPTION                                          | MIN | TYP  | MAX | UNIT |

|--------------------------------------|------------------------------------------------------|-----|------|-----|------|

| 1/T <sub>MCK</sub>                   | Master Clock Frequency                               |     | 2000 |     | kHz  |

| T <sub>MCKH</sub> / T <sub>MCK</sub> | MCLK Duty Cycle for 256 kHz<br>Operation             | 45% |      | 55% |      |

| T <sub>MCKH</sub>                    | Minimum Pulse Width HIGH for MCLK(512 kHz or Higher) | 50  |      |     | ns   |

| T <sub>MCKL</sub>                    | Minimum Pulse Width LOW for MCLK (512 kHz or Higher) | 50  |      |     | ns   |

| T <sub>FTRHM</sub>                   | MCLK falling Edge to FST Rising Edge Hold Time       | 50  |      |     | ns   |

| T <sub>FTRSM</sub>                   | FST Rising Edge to MCLK Falling edge Setup Time      | 50  |      |     | ns   |

| T <sub>RISE</sub>                    | Rise Time for All Digital Signals                    |     |      | 50  | ns   |

| T <sub>FALL</sub>                    | Fall Time for All Digital Signals                    |     |      | 50  | ns   |

Table 8.5 General PCM Timing Parameters

### 9. ABSOLUTE MAXIMUM RATINGS

#### 9.1. ABSOLUTE MAXIMUM RATINGS

| Condition                                                      | Value                                  |

|----------------------------------------------------------------|----------------------------------------|

| Junction temperature                                           | 150°C                                  |

| Storage temperature range                                      | -65°C to +150°C                        |

| Voltage Applied to any pin                                     | $(V_{SS} - 0.3V)$ to $(V_{DD} + 0.3V)$ |

| Voltage applied to any pin (Input current limited to +/-20 mA) | $(V_{SS} - 1.0V)$ to $(V_{DD} + 1.0V)$ |

| V <sub>DD</sub> - V <sub>SS</sub>                              | -0.5V to +6V                           |

<sup>1.</sup> Stresses above those listed may cause permanent damage to the device. Exposure to the absolute maximum ratings may affect device reliability. Functional operation is not implied at these conditions.

#### 9.2. OPERATING CONDITIONS

| Condition                         | Value          |

|-----------------------------------|----------------|

| Industrial operating temperature  | -40°C to +85°C |

| Supply voltage (V <sub>DD</sub> ) | +4.5V to +5.5V |

| Ground voltage (V <sub>SS</sub> ) | 0V             |

<u>Note</u>: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

### 10. ELECTRICAL CHARACTERISTICS

### 10.1. GENERAL PARAMETERS

| Symbol           | Parameters                                      | Conditions                                          | Min (2)               | Typ <sup>(1)</sup> | Max (2) | Units |

|------------------|-------------------------------------------------|-----------------------------------------------------|-----------------------|--------------------|---------|-------|

| $V_{IL}$         | Input LOW Voltage                               |                                                     |                       |                    | 0.6     | V     |

| V <sub>IH</sub>  | Input HIGH Voltage                              |                                                     | 2.4                   |                    |         | V     |

| V <sub>OL</sub>  | PCMT Output LOW Voltage                         | I <sub>OL</sub> = 3 mA                              |                       |                    | 0.4     | V     |

| V <sub>OH</sub>  | PCMT Output HIGH Voltage                        | I <sub>OL</sub> = -3 mA                             | V <sub>DD</sub> – 0.4 |                    |         | V     |

| I <sub>DD</sub>  | V <sub>DD</sub> Current (Operating) - ADC + DAC | No Load                                             |                       | 6                  | 8       | mA    |

| I <sub>SB</sub>  | V <sub>DD</sub> Current (Standby)               | FST & FSR =V <sub>ss</sub> ;<br>PUI=V <sub>DD</sub> |                       | 10                 | 100     | μА    |

| I <sub>pd</sub>  | V <sub>DD</sub> Current (Power Down)            | PUI= V <sub>ss</sub>                                |                       | 0.1                | 10      | μΑ    |

| I <sub>IL</sub>  | Input Leakage Current                           | V <sub>SS</sub> <v<sub>IN<v<sub>DD</v<sub></v<sub>  |                       |                    | +/-10   | μΑ    |

| I <sub>OL</sub>  | PCMT Output Leakage Current                     | V <sub>SS</sub> <pcmt<v<sub>DD</pcmt<v<sub>         |                       |                    | +/-10   | μА    |

|                  |                                                 | High Z State                                        |                       |                    |         |       |

| C <sub>IN</sub>  | Digital Input Capacitance                       |                                                     |                       |                    | 10      | pF    |

| C <sub>OUT</sub> | PCMT Output Capacitance                         | PCMT High Z                                         |                       |                    | 15      | pF    |

<sup>1.</sup> Typical values:  $T_A = 25^{\circ}\text{C}$ ,  $V_{DD} = 5.0 \text{ V}$

<sup>2.</sup> All min/max limits are guaranteed by Winbond via electrical testing or characterization. Not all specifications are 100 percent tested.

### 10.2. ANALOG SIGNAL LEVEL AND GAIN PARAMETERS

$V_{DD}$  =5V  $\pm10\%;\,V_{SS}$  =0V; T  $_A$  =-40  $^{\circ}$ C to +85  $^{\circ}$ C; all analog signals referred to V  $_{AG}$ ; MCLK=BCLK= 2MHz; FST=FSR=8 kHz synchronous operation

| PARAMETER                                                        | SYM.                       | CONDITION                                  | TYP.  |       | ISMIT<br>/D) | _     | EIVE<br>/A) | UNIT      |

|------------------------------------------------------------------|----------------------------|--------------------------------------------|-------|-------|--------------|-------|-------------|-----------|

|                                                                  |                            |                                            |       | MIN.  | MAX.         | MIN.  | MAX.        |           |

| Absolute                                                         | L <sub>ABS</sub>           | 0 dBm0 = 0dBm @ 600Ω                       | 1.096 |       |              |       |             | $V_{PK}$  |

| Level                                                            |                            |                                            | 0.775 |       |              |       |             | $V_{RMS}$ |

| Max. Transmit                                                    | T <sub>XMAX</sub>          | 3.17 dBm0 for μ-Law                        | 1.579 |       |              |       |             | $V_{PK}$  |

| Level                                                            |                            | 3.14 dBm0 for A-Law                        | 1.573 |       |              |       |             | $V_{PK}$  |

| Absolute Gain<br>(0 dBm0 @<br>1020 Hz;<br>T <sub>A</sub> =+25°C) | G <sub>ABS</sub>           | 0 dBm0 @ 1020 Hz;<br>T <sub>A</sub> =+25°C | 0     | -0.25 | +0.25        | -0.25 | +0.25       | dB        |

| Absolute Gain                                                    | G <sub>ABST</sub>          | $T_A=0$ °C to $T_A=+70$ °C                 | 0     | -0.03 | +0.03        | -0.03 | +0.03       | dB        |

| variation with<br>Temperature                                    | variation with Temperature |                                            |       | -0.05 | +0.05        | -0.05 | +0.05       |           |

| Frequency                                                        | G <sub>RTV</sub>           | 15 Hz                                      |       |       | -40          | -0.5  | 0           | dB        |

| Response,                                                        |                            | 50 Hz                                      |       |       | -30          | -0.5  | 0           |           |

| Relative to 0dBm0 @                                              |                            | 60 Hz                                      |       |       | -26          | -0.5  | 0           |           |

| 1020 Hz                                                          |                            | 200 Hz                                     |       | -1.0  | -0.4         | -0.5  | 0           |           |

|                                                                  |                            | 300 to 3000 Hz                             |       | -0.20 | +0.15        | -0.20 | +0.15       |           |

|                                                                  |                            | 3300 Hz                                    |       | -0.35 | +0.15        | -0.35 | +0.15       |           |

|                                                                  |                            | 3400 Hz                                    |       | -0.8  | 0            | -0.8  | 0           |           |

|                                                                  |                            | 3600 Hz                                    |       |       | 0            |       | 0           |           |

|                                                                  |                            | 4000 Hz                                    |       |       | -14          |       | -14         |           |

|                                                                  |                            | 4600 Hz to 100 kHz                         |       |       | -32          |       | -30         |           |

| Gain Variation                                                   | G <sub>LT</sub>            | +3 to -40 dBm0                             |       | -0.3  | +0.3         | -0.2  | +0.2        | dB        |

| vs. Level Tone                                                   |                            | -40 to -50 dBm0                            |       | -0.6  | +0.6         | -0.4  | +0.4        |           |

| (1020 Hz<br>relative to –10<br>dBm0)                             |                            | -50 to -55 dBm0                            |       | -1.6  | +1.6         | -1.6  | +1.6        |           |

### 10.3. ANALOG DISTORTION AND NOISE PARAMETERS

$V_{DD}$  =5V  $\pm10\%;\,V_{SS}$  =0V; T  $_A$  =-40  $^{\circ}$ C to +85  $^{\circ}$ C; all analog signals referred to V  $_{AG}$ ; MCLK=BCLK= 2MHz; FST=FSR=8 kHz synchronous operation

| PARAMETER                                                    | SYM.             | CONDITION            | TRA  | NSMIT ( | (A/D) | REC  | EIVE (C | )/A) | UNIT   |

|--------------------------------------------------------------|------------------|----------------------|------|---------|-------|------|---------|------|--------|

|                                                              |                  |                      | MIN. | TYP.    | MAX.  | MIN. | TYP.    | MAX. |        |

| Total Distortion vs.                                         | $D_{LT\mu}$      | +3 dBm0              | 36   |         |       | 34   |         |      | dBC    |

| Level Tone (1020 Hz,<br>μ-Law, C-Message                     |                  | 0 dBm0 to -30 dBm0   | 36   |         |       | 36   |         |      |        |

| Weighted)                                                    |                  | -40 dBm0             | 29   |         |       | 30   |         |      |        |

|                                                              |                  | -45 dBm0             | 25   |         |       | 25   |         |      |        |

| Total Distortion vs.                                         | $D_{LTA}$        | +3 dBm0              | 36   |         |       | 34   |         |      | dBp    |

| Level Tone (1020 Hz, A-Law, Psophometric                     |                  | 0 dBm0 to -30 dBm0   | 36   |         |       | 36   |         |      |        |

| Weighted)                                                    |                  | -40 dBm0             | 29   |         |       | 30   |         |      |        |

|                                                              |                  | -45 dBm0             | 25   |         |       | 25   |         |      |        |

| Spurious Out-Of-Band                                         | $D_{SPO}$        | 4600 Hz to 7600 Hz   |      |         |       |      |         | -30  | dB     |

| at RO+ (300 Hz to 3400 Hz @ 0dBm0)                           |                  | 7600 Hz to 8400 Hz   |      |         |       |      |         | -40  |        |

| 0 100 112 @ 00B1110)                                         |                  | 8400 Hz to 100000 Hz |      |         |       |      |         | -30  |        |

| Spurious In-Band (700<br>Hz to 1100 Hz @<br>0dBm0)           | D <sub>SPI</sub> | 300 to 3000 Hz       |      |         | -47   |      |         | -47  | dB     |

| Intermodulation Distortion (300 Hz to 3400 Hz -4 to -21 dBm0 | D <sub>IM</sub>  | Two tones            |      |         | -41   |      |         | -41  | dB     |

| Crosstalk (1020 Hz @ 0dBm0)                                  | D <sub>XT</sub>  |                      |      |         | -75   |      |         | -75  | dBm0   |

| Absolute Group Delay                                         | $	au_{ABS}$      | 1200Hz               |      |         | 360   |      |         | 240  | μsec   |

| Group Delay                                                  | $\tau_{D}$       | 500 Hz               |      |         | 750   |      |         | 750  | μsec   |

| Distortion (relative to group delay @ 1200                   |                  | 600 Hz               |      |         | 380   |      |         | 370  |        |

| Hz)                                                          |                  | 1000 Hz              |      |         | 130   |      |         | 120  |        |

|                                                              |                  | 2600 Hz              |      |         | 130   |      |         | 120  |        |

|                                                              |                  | 2800 Hz              |      |         | 750   |      |         | 750  |        |

| Idle Channel Noise                                           | N <sub>IDL</sub> | μ-Law; C-message     |      |         | 18    |      |         | 13   | dBrnc0 |

|                                                              |                  | A-Law; Psophometric  |      |         | -68   |      |         | -78  | dBm0p  |

### 10.4. ANALOG INPUT AND OUTPUT AMPLIFIER PARAMETERS

$V_{DD}\text{=}5V~\pm10\%;~V_{SS}\text{=}0V;~T_{A}\text{=-}40^{\circ}\text{C}$  to +85°C; all analog signals referred to  $V_{AG};$

| PARAMETER                                  | SYM.                | CONDITION                          | MIN.  | TYP.  | MAX.                 | UNIT. |

|--------------------------------------------|---------------------|------------------------------------|-------|-------|----------------------|-------|

| Al Input Offset Voltage                    | $V_{OFF,AI}$        | Al+, Al-                           |       |       | ±25                  | mV    |

| Al Input Current                           | I <sub>IN,AI</sub>  | Al+, Al-                           |       | ±0.1  | ±1.0                 | μА    |

| Al Input Resistance                        | R <sub>IN,AI</sub>  | AI+, AI- to V <sub>AG</sub>        | 10    |       |                      | MΩ    |

| Al Input Capacitance                       | C <sub>IN,AI</sub>  | Al+, Al-                           |       |       | 10                   | pF    |

| Al Common Mode Input Voltage<br>Range      | V <sub>CM,AI</sub>  | AI+, AI-                           | 1.2   |       | V <sub>DD</sub> -1.2 | V     |

| Al Common Mode Rejection Ratio             | CMRR <sub>TI</sub>  | AI+, AI-                           |       | 60    |                      | dB    |

| Al Amp Gain Bandwidth Product              | $GBW_TI$            | AO, R <sub>LD</sub> ≥10kΩ          |       | 2150  |                      | kHz   |

| Al Amp DC Open Loop Gain                   | G <sub>TI</sub>     | AO, R <sub>LD</sub> ≥10kΩ          |       | 95    |                      | dB    |

| Al Amp Equivalent Input Noise              | N <sub>TI</sub>     | C-Message Weighted                 |       | -24   |                      | dBrnC |

| AO Output Voltage Range                    | $V_{TG}$            | $R_{LD}$ =10k $\Omega$ to $V_{AG}$ | 0.5   |       | V <sub>DD</sub> -0.5 | V     |

|                                            |                     | $R_{LD}$ =2k $\Omega$ to $V_{AG}$  | 1.0   |       | V <sub>DD</sub> -1.0 |       |

| Load Resistance                            | R <sub>LDTGRO</sub> | AO, RO to V <sub>AG</sub>          | 2     |       |                      | kΩ    |

| Load Capacitance                           | C <sub>LDTGRO</sub> | AO, RO                             |       |       | 100                  | рF    |

| AO & RO Output Current                     | I <sub>OUT1</sub>   | 0.5 ≤AO,RO+≤ V <sub>DD</sub> -0.5  | ±1.0  |       |                      | mA    |

| RO+ Output Resistance                      | R <sub>RO+</sub>    | RO+, 0 to 3400 Hz                  |       | 1     |                      | Ω     |

| RO+ Output Offset Voltage                  | $V_{OFF,RO+}$       | RO+ to V <sub>AG</sub>             |       |       | ±25                  | mV    |

| Analog Ground Voltage                      | $V_{AG}$            | Relative to V <sub>SS</sub>        | 2.429 | 2.5   | 2.573                | V     |

| V <sub>AG</sub> Output Resistance          | R <sub>VAG</sub>    | Within ±25mV change                |       | 2.5   | 12.5                 | Ω     |

| Power Supply Rejection Ratio (0            | PSRR                | Transmit                           | 40    | 80    |                      | dBC   |

| to 100 kHz to V <sub>DD</sub> , C-message) |                     | Receive                            | 40    | 75    |                      |       |

| PAI Input Offset Voltage                   | $V_{OFF,PAI}$       | PAI                                |       |       | ±20                  | mV    |

| PAI Input Current                          | I <sub>IN,PAI</sub> | PAI                                |       | ±0.05 | ±1.0                 | μΑ    |

| PAI Input Resistance                       | R <sub>IN,PAI</sub> | PAI to V <sub>AG</sub>             | 10    |       |                      | MΩ    |

| PAI Amp Gain Bandwidth<br>Product          | GBW <sub>PI</sub>   | PAO- no load                       |       | 1000  |                      | kHz   |

| Output Offset Voltage                      | $V_{OFF,PO}$        | PAO+ to PAO-                       |       |       | ±50                  | mV    |

| Load Resistance                            | R <sub>LDPO</sub>   | PAO+, PAO-<br>differentially       | 300   |       |                      | Ω     |

| Load Capacitance                           | C <sub>LDPO</sub>   | PAO+, PAO-<br>differentially       |       |       | 1000                 | pF    |

### W681513

| PARAMETER                                                    | SYM.               | CONDITION                                             | MIN.  | TYP. | MAX. | UNIT. |

|--------------------------------------------------------------|--------------------|-------------------------------------------------------|-------|------|------|-------|

| PO Output Current                                            | I <sub>OUTPO</sub> | 0.5 ≤AO,RO+≤ V <sub>DD</sub> -0.5                     | ±10.0 |      |      | mA    |

| PO Output Resistance                                         | R <sub>PO</sub>    | PAO+ to PAO-                                          |       | 1    |      | Ω     |

| PO Differential Gain                                         | G <sub>PO</sub>    | R <sub>LD</sub> =300Ω, +3dBm0, 1<br>kHz, PAO+ to PAO- | -0.2  | 0    | +0.2 | dB    |

| PO Differential Signal to                                    | D <sub>PO</sub>    | Z <sub>LD</sub> =300Ω                                 | 45    | 60   |      | dBC   |

| Distortion C-Message weighted                                |                    | $Z_{LD}$ =100nF + 100 $\Omega$                        |       | 40   |      |       |

|                                                              |                    | $Z_{LD}$ =100nF + 20 $\Omega$                         |       | 40   |      |       |

| PO Power Supply Rejection                                    | PSRR <sub>P</sub>  | 0 to 4 kHz                                            | 40    | 55   |      | dB    |

| Ratio (0 to 25 kHz to V <sub>DD</sub> ,<br>Differential out) | 0                  | 4 to 25 kHz                                           |       | 40   |      |       |

### **10.5. DIGITAL I/O**

### 10.5.1. $\mu$ -Law Encode Decode Characteristics

| Normalized         | μ _α |       |       |         |      |      |      |      | Normalized |

|--------------------|------|-------|-------|---------|------|------|------|------|------------|

| Encode             |      |       |       | Digital | Code |      |      |      | Decode     |

| Decision<br>Levels | D7   | D6    | D5    | D4      | D3   | D2   | D1   | D0   | Levels     |

| 2010.0             | Sign | Chord | Chord | Chord   | Step | Step | Step | Step |            |

| 8159               |      |       |       |         |      |      |      |      |            |

| 7903               | 1    | 0     | 0     | 0       | 0    | 0    | 0    | 0    | 8031       |

| 1903               |      |       |       |         |      |      |      |      | :          |

| 4319               | 1    | 0     | 0     | 0       | 1    | 1    | 1    | 1    | 4191       |

| 4063               |      |       |       |         |      |      |      |      | :          |

| 2143               | 1    | 0     | 0     | 1       | 1    | 1    | 1    | 1    | 2079       |

| 2015               |      |       |       |         |      |      |      |      | :          |

| 1055               | 1    | 0     | 1     | 0       | 1    | 1    | 1    | 1    | 1023       |

| 991                |      |       | 1     |         |      | 1    | 1    | •    | :          |

| 511                | 1    | 0     | 1     | 1       | 1    | 1    | 1    | 1    | 495        |

| 479<br>:           |      | l     |       | l       |      |      |      | 1    | :          |

| 239                | 1    | 1     | 0     | 0       | 1    | 1    | 1    | 1    | 231        |

| 223                |      |       |       |         |      |      |      |      | :          |

| 103                | 1    | 1     | 0     | 1       | 1    | 1    | 1    | 1    | 99         |

| 95<br>:            |      |       |       |         |      |      |      |      | :          |

| 35                 | 1    | 1     | 1     | 0       | 1    | 1    | 1    | 1    | 33         |

| <b>31</b>          |      |       |       |         |      |      |      |      | :          |

| 3                  | 1    | 1     | 1     | 1       | 1    | 1    | 1    | 0    | 2          |

| 1                  | 1    | 1     | 1     | 1       | 1    | 1    | 1    | 1    | 0          |

| 0                  |      | ı     | 1     | ı       |      | 1    | 1    | ı    | •          |

### Notes:

Sign bit = 0 for negative values, sign bit = 1 for positive values

### 10.5.2. A-Law Encode Decode Characteristics

| Normalized             |          |       |       | Digital | Code |      |      |      | Normalized |

|------------------------|----------|-------|-------|---------|------|------|------|------|------------|

| Encode                 | D7       | D6    | D5    | D4      | D3   | D2   | D1   | D0   | Decode     |

| Decision<br>Levels     | Sign     | Chord | Chord | Chord   | Step | Step | Step | Step | Levels     |

|                        |          |       |       |         |      |      |      |      |            |

| 4096                   | 1        | 0     | 1     | 0       | 1    | 0    | 1    | 0    | 4032       |

| 3968                   |          |       |       |         |      |      |      |      | :          |

| 2048                   |          | T     | T     | T       | T    | T    |      |      |            |

| 2048                   | 1        | 0     | 1     | 0       | 0    | 1    | 0    | 1    | 2112       |

| :                      |          |       |       |         |      |      |      |      | :          |

| 1088                   | 1        | 0     | 1     | 1       | 0    | 1    | 0    | 1    | 1056       |

| 1024                   |          | I     |       | I       |      |      |      |      | :          |

| 544                    |          |       |       |         |      |      |      |      |            |

| 5 <del>44</del><br>512 | 1        | 0     | 0     | 0       | 0    | 1    | 0    | 1    | 528        |

| 312                    |          |       |       |         |      |      |      |      | :          |

| 272                    | 1        | 0     | 0     | 1       | 0    | 1    | 0    | 1    | 264        |

| 256                    | <u> </u> |       |       | -       |      | -    |      |      | :          |

| :                      |          |       |       |         |      |      |      |      |            |

| 136                    | 1        | 1     | 1     | 0       | 0    | 1    | 0    | 1    | 132        |

| 128                    |          |       |       |         |      |      |      |      | :          |

| 68                     | 1        | 1     | 1     | 0       | 0    | 1    | 0    | 1    | 66         |

| 64                     | - '      | '     | '     |         |      | '    |      |      | :          |

| :                      |          |       |       |         |      |      |      |      |            |

| 2                      | 1        | 1     | 0     | 1       | 0    | 1    | 0    | 1    | 1          |

| 0                      |          | I     | I     | I       | I    | I    |      | 1    | ı          |

#### Notes:

- 1. Sign bit = 0 for negative values, sign bit = 1 for positive values

- 2. Digital code includes inversion of all even number bits

### 10.5.3. PCM Codes for Zero and Full Scale

|              |          | μ-Law      |               | A-Law    |            |               |  |

|--------------|----------|------------|---------------|----------|------------|---------------|--|

| Level        | Sign bit | Chord bits | Step bits     | Sign bit | Chord bits | Step bits     |  |

|              | (D7)     | (D6,D5,D4) | (D3,D2,D1,D0) | (D7)     | (D6,D5,D4) | (D3,D2,D1,D0) |  |

| + Full Scale | 1        | 000        | 0000          | 1        | 010        | 1010          |  |

| + Zero       | 1        | 111        | 1111          | 1        | 101        | 0101          |  |

| - Zero       | 0        | 111        | 1111          | 0        | 101        | 0101          |  |

| - Full Scale | 0        | 000        | 0000          | 0        | 010        | 1010          |  |

### 10.5.4. PCM Codes for 0dBm0 Output

|        |          | μ-Law      |               | A-Law    |            |               |  |

|--------|----------|------------|---------------|----------|------------|---------------|--|

| Sample | Sign bit | Chord bits | Step bits     | Sign bit | Chord bits | Step bits     |  |

|        | (D7)     | (D6,D5,D4) | (D3,D2,D1,D0) | (D7)     | (D6,D5,D4) | (D3,D2,D1,D0) |  |

| 1      | 0        | 001        | 1110          | 0        | 011        | 0100          |  |

| 2      | 0        | 000        | 1011          | 0        | 010        | 0001          |  |

| 3      | 0        | 000        | 1011          | 0        | 010        | 0001          |  |

| 4      | 0        | 001        | 1110          | 0        | 011        | 0100          |  |

| 5      | 1        | 001        | 1110          | 1        | 011        | 0100          |  |

| 6      | 1        | 000        | 1011          | 1        | 010        | 0001          |  |

| 7      | 1        | 000        | 1011          | 1        | 010        | 0001          |  |

| 8      | 1        | 001        | 1110          | 1        | 011        | 0100          |  |

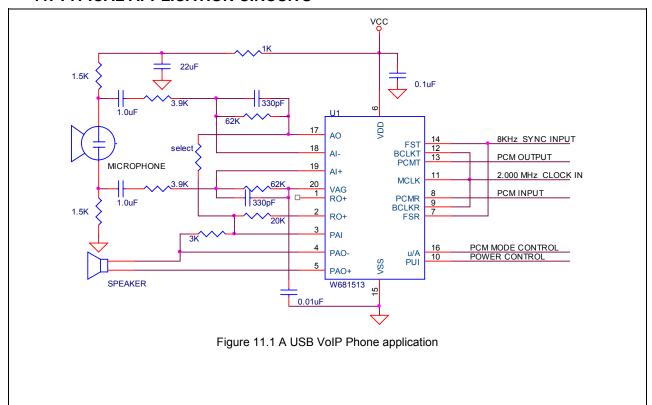

### 11. TYPICAL APPLICATION CIRCUITS

### winbond

### SUGGESTED COMPONENT VALUES BY APPLICATION

| SCHEMATIC<br>COMPONENT # | TELEPHONE<br>HANDSET | VoIP PHONE<br>SET |

|--------------------------|----------------------|-------------------|

| R3,4                     | 1K                   | 1K                |

| R5,6                     | 27K                  | 91K               |

| C6,7                     | 1200 pF              | 330 pF            |

| R9                       | SELECT               | SELECT            |

| R7                       | 20K                  | 20K               |

| R8                       | 3K                   | 3K                |

In the handset application the gain from the handset microphone is set to 27 for the input amplifier. This is because the acoustical chamber in the telephone type handset lets the electret microphone provide an output of ~28 mV<sub>RMS</sub>. The chamber typically has a gain of 3 over a bare microphone (or one placed with only a small opening to the outside world.) Because of the high sensitivity of the earphone (150  $\Omega$  impedance) in a typical handset, the output gain from the Power Amp is set to ~0.16 for a satisfactory listening level.

In the VoIP telephone, or small wireless phones, the plastic case is typically too small to provide a reasonable acoustic chamber. Thus the output from the microphone is less than in the previous example. This results in having to set the input gain of the CODEC to  $\sim$ 75 to 90 and in a comparable

signal level to the receive telephone handset but, because of the increased gain, the Signal-to-Noise Ratio (SNR) has decreased and the signal sounds noisier. On the receive side, the gain is set as in the previous example. When the Power Amp gain is as low as 0.16 a 32 ohm load speaker can be driven.

Resistor R9 sets the sidetone level (the signal fed back to the earpiece from the microphone so the telephone sounds "live") to the level desired by the designer.

Capacitors C6 and C7 are introduced for external compensation to keep the input amplifier stable at such high gain figures and prevent oscillation. These capacitors are not needed when the gain is close to unity or less than unity.

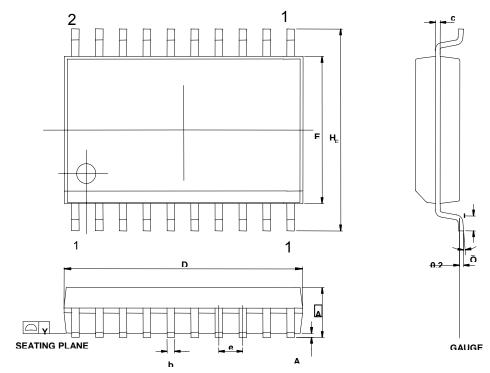

### 12. PACKAGE SPECIFICATION

### 12.2. 20L SOP (SOG)-300MIL

SMALL OUTLINE PACKAGE (SAME AS SOG & SOIC) DIMENSIONS

| 0.450          | DIMENS | ION (MM) | DIMENS    | SION (INCH) |  |

|----------------|--------|----------|-----------|-------------|--|

| SYMBOL         | MIN.   | MAX.     | MIN.      | MAX.        |  |

| Α              | 2.35   | 2.65     | 0.093     | 0.104       |  |

| A1             | 0.10   | 0.30     | 0.004     | 0.012       |  |

| b              | 0.33   | 0.51     | 0.013     | 0.020       |  |

| С              | 0.23   | 0.32     | 0.009     | 0.013       |  |

| Е              | 7.40   | 7.60     | 0.291     | 0.299       |  |

| D              | 12.60  | 13.00    | 0.496     | 0.512       |  |

| е              | 1.27   | BSC      | 0.050 BSC |             |  |

| H <sub>E</sub> | 10.00  | 10.65    | 0.394     | 0.419       |  |

| Y              | -      | 0.10     | -         | 0.004       |  |

| L              | 0.40   | 1.27     | 0.016     | 0.050       |  |

| θ              | 0°     | 8°       | 0°        | 8°          |  |

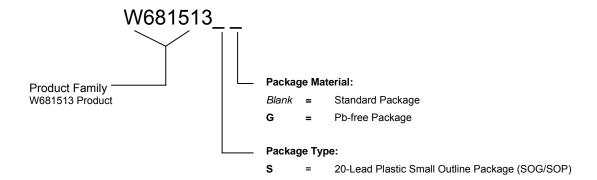

### 13. ORDERING INFORMATION

Winbond Part Number Description

When ordering W681513 series devices, please refer to the following part numbers.

| Part Number |  |

|-------------|--|

| W681513S    |  |

| W681513SG   |  |

### **14. VERSION HISTORY**

| VERSION              | DATE               | PAGE    | DESCRIPTION                                                       |

|----------------------|--------------------|---------|-------------------------------------------------------------------|

| A3                   | October 1,<br>2003 |         | First published version                                           |

| A10                  | April 2005         | 33      | Add Important Notice                                              |

| A11 October,<br>2005 |                    | 2       | Added reference to Pb-free RoHS packaging and to $V_{\text{RMS}}$ |

|                      |                    | Various | Capitalized logic HIGH/LOW                                        |

|                      |                    | 22      | Added Reference to V <sub>RMS</sub>                               |

|                      |                    | 22, 23  | Extended Test conditions                                          |

|                      |                    | 23      | Corrected Idle Channel Noise min/max and units.                   |

|                      |                    | 29-31   | Improved Application Diagrams                                     |

|                      |                    | 33      | Added G package ordering code                                     |

### **Important Notice**

Winbond products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further more, Winbond products are not intended for applications wherein failure of Winbond products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

The information contained in this datasheet may be subject to change without notice. It is the responsibility of the customer to check the Winbond USA website (<a href="https://www.winbond-usa.com">www.winbond-usa.com</a>) periodically for the latest version of this document, and any Errata Sheets that may be generated between datasheet revisions.

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.